|

Q1.ディジタルな表現は、「量を数で表す」表現ということですが、「数」ということでいえば、必ずしも2進数で表す必要はないのでありませんか? Q2.電圧が高い低いで、それぞれ1と0を表すということですが、電圧がちょうど境界の値のときには値はどうなるのですか? Q3.2の補数表示で表される数は、負の数のほうが1つ多いのでしょうか? Q4.Nビットの乗算で、最後にNビット目の乗算結果を引くということですが、乗数が正または0のときは必要ないのではありませんか? Q5.Nビットの乗算の結果は2Nビットになります。これを繰り返すと、かけ算のたびに桁数が大きくなって、計算できなくなりませんか? Q6.ブール代数やMIL記法による表現では、一つの論理関数を表現するやりかたが複数あるように思います。正しいのでしょうか? Q7.ブール代数があればMIL記法は必要ないのではありませんか? Q8.N入力のXOR(N≧3)はどのように定義されるのですか? Q9.{NAND}が完備であれば、NAND以外の論理素子を考える必要はないのではありませんか?(NORも同様) Q10.組合せ回路は加法標準形で与えられるもので十分ではないのですか? Q11.組合せ回路の簡単化としてあげられている、ブール代数による方法とカルノー図による方法はアルゴリズムになっておらず、きちんとした方法には見えないのですが? Q12.カルノー図で両端がつながっているというのがイメージしづらいのですが。 Q13.6入力以上のカルノー図を書くことはできますか? Q14.カルノー図によって簡単化した結果が一通りではない場合もあるようですが? Q15.出力が2つ以上あるとき、それぞれの出力についてカルノー図を書いて簡単化するだけでいいのですか? Q16.Nビット加算器の最下位の桁の計算は、半加算器でよいのではありませんか? Q17.Nビット加算器を、1ビット全加算器から作るのではなく、はじめから2×N入力の組合せ回路として設計してはいけないのですか? Q18.Nビット加減算器でBの入力にXORを使うのはなぜですか? Q19.74381型ALUの回路はどのようなものですか? Q20.今回学んだエンコーダでは、入力に対する優先度が固定されていますが、入力のたびに優先度が変更されるように作れないのですか? Q21.ゲートのないラッチは、順序回路として意味がないのではありませんか? Q22.順序回路としてクロックでゲートするフリップフロップが使えるように、回路にフィードバックがないように作ることはできないのですか? Q23.マスタスレーブ型フリップフロップがあれば、エッジトリガ型フリップフロップは不要ではありませんか? Q24.JKラッチは考えられませんか? Q25.JKフリップフロップがあればTフリップフロップは不要ではありませんか? Q26.分周とは何ですか? Q27.非同期カウンタでパルスが問題になるのはどのような場合ですか? Q28.同期10進カウンタにおいてフリップフロップFF0とFF2の出力が通常の16進カウンタと同じ動作とはどのような意味ですか? Q29.非同期10進カウンタにおいて、どうしてFF0とFF3のQが1の時(D0=1, D3=1の時)にFF3を反転するのですか? Q30.どうしてコンピュータ間の通信でPISOとSIPOを利用するのですか? Q31.ミーリーグラフ以外に状態遷移図を表現する方法がありますか? Q32.nextSとは何ですか? Q33.状態遷移表からミーリーグラフへの変換の方法を教えてください。 Q34.状態Aと状態Bのそれぞれを1, 0 としていますが、これらを 0, 1 としても良いのですか? Q35.論理式からどのように順序回路を生成すればよいのですか? Q36.電圧降下とは何ですか? Q37.現在、Diode Transistor Logic (DTL) は利用されているのですか? Q38.現在、Transistor Transistor Logic (TTL) は利用されているのですか? Q39.どうして図の構成をワイヤードORと呼ぶのですか? Q40.高インピーダンスとはどのような状態ですか? Q41.読み書きできるメモリはRAMと表記されますが、Read Write Memory ではいけないのですか? Q42.電荷を取り出した(読み出した)メモリセルの記憶内容が失われると困ったことになりませんか? Q43.RAS, CAS にアッパーライン(否定)が付いているのはなぜですか? Q44.DRAMではどうしてRASとCASを用いる必要があるのですか? Q45.最新のDRAMにおける高速化の工夫にはどのようなものがありますか? Q46.フォンノイマン型ではないコンピュータとはどのようなものですか? Q47.命令の長さは32ビット程度と説明されていますが、32ビット以外にどのような形式がありますか? Q48.算術論理演算命令、メモリ操作命令、分岐命令の他にどのような命令があるのですか? Q49.命令フェッチは1つの命令を読み出すと説明されていますが、複数の命令を同時に読み出す(フェッチする)ことはないのですか? Q50.命令メモリとデータメモリとして個別のメモリが用いられていますが、1つのメモリを共有して利用してはいけないのですか? Q51.パイプライン処理とは何ですか? Q1 ディジタルな表現は、「量を数で表す」表現ということですが、「数」ということでいえば、必ずしも2進数で表す必要はないのでありませんか? A1 その通りです。3進数や10進数で表してもかまいません。今のディジタル回路で2進数が広く用いられているのは、電圧の「高い」「低い」だけで各桁の数字を表せるため、簡単でエラーが起こりにくいからです。信号線ごとに、電圧の高低のレベルを細かく設定すれば、3進数以上の表し方が可能になりますが、現在の普通のディジタル回路ではこれは使われていません。 Q2 電圧が高い低いで、それぞれ1と0を表すということですが、電圧がちょうど境界の値のときには値はどうなるのですか? A2 ディジタル回路は、決められた電圧の範囲で1または0をとりますが、境界領域の電圧では値が定義できなくなってしまいます。値を確定したい時点では、必ず1か0かが確定する電圧になっている必要があります。 Q3 2の補数表示で表される数は、負の数のほうが1つ多いのでしょうか? A3 はい。たとえば4ビットで表される数は、負の数が1000から1111まで(10進数で-8から-1まで)、正の数が0001から0111(10進数で1から7まで)と、負の数のほうが1つ多いのです。これは、絶対値が1つ大きな値まで表せるからです。 Q4 Nビットの乗算で、最後にNビット目の乗算結果を引くということですが、乗数が正または0のときは必要ないのではありませんか? A4 必ずしも必要ではありません。ただし、その場合には、「正負を判定してから引き算をするかどうか決める」ことになります。ここで示した方法は、「正負の判定なしに引き算を実行する」ことで、判定にかかる手間を省いています。 Q5 Nビットの乗算の結果は2Nビットになります。これを繰り返すと、かけ算のたびに桁数が大きくなって、計算できなくなりませんか? A5 原理的にはそうですが、実際には、決められた桁数で表現できる範囲で計算を進め、これがあふれたら例外として処理します。この範囲でおさまらない大きな数を扱いたいときには、浮動小数点表記など別の方法を使います。 Q6 ブール代数やMIL記法による表現では、一つの論理関数を表現するやりかたが複数あるように思います。正しいのでしょうか? A6 正しいのです。与えられた論理関数に対して、真理値表は一意に決まりますが、ブール代数やMIL記法による表現は2種類以上あるのが一般的です。 Q7 ブール代数があればMIL記法は必要ないのではありませんか? A7 MIL記法は、ブール代数よりも実際の回路に近い表現法で、設計の際には役に立つことが多いのです。どんな素子を使うか、素子をどういう順番で接続するかなど、ブール代数では十分に表現されていないものを具体化することができる利点があります。 Q8 N入力のXOR(N≧3)はどのように定義されるのですか? A8 入力のうち、1の数が奇数のときに出力が1、偶数のときに出力が0となる論理関数として定義されます。 Q9 {NAND}が完備であれば、NAND以外の論理素子を考える必要はないのではありませんか?(NORも同様) A9 たしかにNAND(またはNOR)だけですべての論理関数を実現することができますが、回路規模や設計の簡単さなどの点で他の素子を使ったほうがいい場合が多いのです。 Q10 組合せ回路は加法標準形で与えられるもので十分ではないのですか? A10 入力の数が少ない場合などは、加法標準形で問題ないこともあります。しかし、一般に加法標準形をそのまま組合せ回路にすると、素子数が多く複雑なものになる欠点があります。 Q11 組合せ回路の簡単化としてあげられている、ブール代数による方法とカルノー図による方法はアルゴリズムになっておらず、きちんとした方法には見えないのですが? A11 「論理的隣接性に着目して関数を簡単化する」ということで、厳密には、隣接性のある組合せをすべて試すことで、アルゴリズム化できることになります。これをやったのが、クワイン・マクラスキーによる方法です。 Q12 カルノー図で両端がつながっているというのがイメージしづらいのですが。 A12 図は2次元の表で描かれますが、実際には下のように閉じた曲面となっています(4入力の場合)。一度こうした曲面をイメージしてみるとよいと思います。  Q13 6入力以上のカルノー図を書くことはできますか? A13 6入力のカルノー図は、4入力のカルノー図を上下に4枚重ねることで書いて利用することができます。7入力以上になると、3次元に収まらず、実用的ではなくなります。 Q14 カルノー図によって簡単化した結果が一通りではない場合もあるようですが? A14 はい。最終的にくくったループの大きさと数が同じになるものが2通り以上出る場合があります。 例を下に記します。

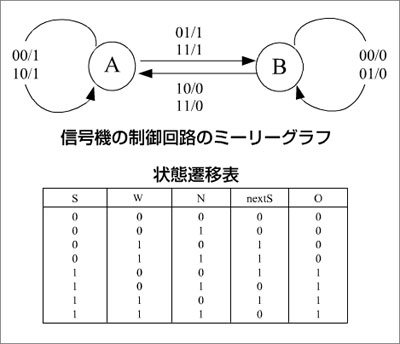

Q15 出力が2つ以上あるとき、それぞれの出力についてカルノー図を書いて簡単化するだけでいいのですか? A15 それぞれのカルノー図に共通するループがあれば、これに対応するAND素子を共有することでさらに簡単化することができます。 Q16 Nビット加算器の最下位の桁の計算は、半加算器でよいのではありませんか? A16 その通りです。桁上げ入力は必要ありません。なお、市販品やライブラリなどでは、これを組み合わせてさらに桁数の多い加算器を作ることを考えており、そのために桁上げ入力を設けていることが多いようです。 Q17 Nビット加算器を、1ビット全加算器から作るのではなく、はじめから2×N入力の組合せ回路として設計してはいけないのですか? A17 構いませんし、そのほうが回路規模や動作速度の点で優れた回路ができると考えられます。しかし、Nが大きくなるとカルノー図を使った設計ができなくなりますし、回路の簡単化にも時間がかかるようになります。この場合、単純な回路を組み合わせ、キャリルックアヘッドなどの高速化をするなどの工夫が有効になります。 Q18 Nビット加減算器でBの入力にXORを使うのはなぜですか? A18 S/Aが0のときに、Bを通し、S/Aが1のときにB'+1(ただしB'はBの全ビットを反転させたもの)を通すことで、加算・減算が使い分けられるようにするためです。 Q19 74381型ALUの回路はどのようなものですか? A19  TEXAS INSTRUMENTS DATASHEET SDLS168 - JANUARY 1981 - REVISED MARCH 1988 より抜粋 Q20 今回学んだエンコーダでは、入力に対する優先度が固定されていますが、入力のたびに優先度が変更されるように作れないのですか? A20 組合せ回路は、過去の入力によって出力を変えることはできませんので、このようなエンコーダを組合せ回路として作ることができません。順序回路ならば作ることができます。 Q21 ゲートのないラッチは、順序回路として意味がないのではありませんか? A21 ゲートのないDラッチは入力を遅延して出力するだけですが、ゲートのないSRラッチは、S=0, R=0のときに「値を保持する」機能があり、順序回路として意味があります。 Q22 順序回路としてクロックでゲートするフリップフロップが使えるように、回路にフィードバックがないように作ることはできないのですか? A22 順序回路は、「今の状態と入力」から「次の状態と出力」を作る回路です。「次の状態」が「今の状態」に依存しているかぎり、フィードバックは存在することになります。 Q23 マスタスレーブ型フリップフロップがあれば、エッジトリガ型フリップフロップは不要ではありませんか? A23 マスタスレーブ型フリップフロップでは、クロックがオンの間信号を保持する必要があり、クロックの立ち上がりだけで動作するエッジトリガ型ほど高速に動作できない場合があります。 Q24 JKラッチは考えられませんか? A24 回路としては考えられますが、J=1, K=1のときに発振します。これを禁止入力とするとSRラッチと同じ動作になり、あえてこれを考える必要がなくなります。 Q25 JKフリップフロップがあればTフリップフロップは不要ではありませんか? A25 その通りですが、値を反転させる動作だけを行うフリップフロップを考えることで、回路の動作がよりはっきりすることがあります。そのための便法としてTフリップフロップがあると考えてよいでしょう。 Q26 分周とは何ですか? A26 (誤記があったため削除) Q27 非同期カウンタでパルスが問題になるのはどのような場合ですか? A27 例えば, 立ち上がりエッジでカウントアップするカウンタの入力にD1を接続する場合には、このパルスによって誤ったカウントアップが生じてしまいます。 Q28 同期10進カウンタにおいてフリップフロップFF0とFF2の出力が通常の16進カウンタと同じ動作とはどのような意味ですか? A28 同期16進カウンタにおけるフリップフロップFF0とFF2と同様に、「次のクロックのエッジで出力が変化するのは、下位の桁がすべて1になったとき」という原理に基づいて動作することを意味します。 Q29 非同期10進カウンタにおいて、どうしてFF0とFF3のQが1の時(D0=1, D3=1の時)にFF3を反転するのですか? A29 10進カウンタのタイミング図を見てください。カウンタの値が9の時に、カウンタの値をリセットすればよいので、D0=1, D1=0, D2=0, D3=1 の時に反転しても良いのですが、これは冗長です。カウンタの値が0から9の時のD0とD3を良く見ると、カウンタの値が9となって初めて D0=1, D3=1 となることがわかります。このため、D0=1, D3=1 という条件を用いて反転すれば良いのです。 Q30 どうしてコンピュータ間の通信でPISOとSIPOを利用するのですか? A30 コンピュータ間の電線の本数を減らしたい場合などに、1ビットずつ逐次的にデータを送信するシリアル通信が利用されます。この場合に、データをシリアルに変換するためにPISOを、シリアルから並列に変換するためにSIPOが利用されます。 Q31 ミーリーグラフ以外に状態遷移図を表現する方法がありますか? A31 ミーリーグラフとして表現されるミーリー型順序機械の他に、ムーア型順序機械を用いて表現する方法などがあります。 Q32 nextSとは何ですか? A32 Sの次の状態のことをnextSと記述しています。この順序回路では、Q'とIとのANDを取ったものがDフリップフロップの入力となっていますので、これがクロックと同期して更新される次状態nextSとなります。 Q33 状態遷移表からミーリーグラフへの変換の方法を教えてください。 A33 状態0で入力が0の時、次状態が0で出力が0です。これは、左端の矢印に対応します。状態0で入力が1の時、次状態が1で出力が0です。これは、状態0から状態1への矢印に対応します。状態1で入力が0の時、次状態が0で出力が0です。また、状態1で入力が1の時、次状態が0で出力が1です。これらは、状態1から状態0への矢印に対応します。このように、状態遷移表の1行に対応する矢印を書き込んでいくことでミーリーグラフを作成できます。  Q34

Q34状態Aと状態Bのそれぞれを1, 0 としていますが、これらを 0, 1 としても良いのですか? A34 問題ありません。ただし、これらの符号化のやり方によって得られる論理式と回路が異なるものとなりますので注意が必要です。  Q35 論理式からどのように順序回路を生成すればよいのですか? A35 O = S という式から、フリップフロップの出力Sと出力線Oを接続すればよいことがわかります。また、nextS = S' W + S N' という式から、フリップフロップの入力 nextS は、Sの否定である Q' と W のANDを取ったものと、S とN'のANDを取ったものとのORとなっていることがわかります。  Q36

Q36電圧降下とは何ですか? A36 ある回路に電流が流れるときに、その回路の電気抵抗の両端に電位差が生じる現象のことを電圧降下と呼びます。 Q37 現在、Diode Transistor Logic (DTL) は利用されているのですか? A37 Diode Transistor Logic には、電圧降下が起こって期待する動作が得られない、ダイオードの低電位の出力でトランジスタが誤動作する、ドライブ能力が低い、などの問題点があります。このため、現在は利用されなくなっています。 Q38 現在、Transistor Transistor Logic (TTL) は利用されているのですか? A38 Transistor Transistor Logic は74シリーズなどとして広く利用されてきました。しかしながら、CMOSと比較して、消費電力が大きく、集積度を高くできないといった欠点から利用範囲が減っています。 Q39 どうして図の構成をワイヤードORと呼ぶのですか? A39 このような回路は前段の各出力のANDをとった値が最終的な出力となります。このため、ワイヤードAND回路と呼ぶのが正しいかもしれないのですが、バスでは低い電位を1に対応させる負論理がとられることが多いために、慣例としてワイヤードORと呼ばれています。 Q40 高インピーダンスとはどのような状態ですか? A40 回路の出力が電気的に切り離された状態(電気的に絶縁された状態)を高インピーダンスまたはハイ・インピーダンスと呼びます。 Q41 読み書きできるメモリはRAMと表記されますが、Read Write Memory ではいけないのですか? A41 読み出し専用のメモリはRead Only Memory (ROM) と呼ばれます。これに対する用語としては、Read Write Memory が適切かもしれませんが、歴史的に、読み書きできるメモリはRandom Access Memory (RAM) と呼ばれます。 Q42 電荷を取り出した(読み出した)メモリセルの記憶内容が失われると困ったことになりませんか? A42 DRAMでは、メモリセルからデータを読み出すことで、そのメモリセルの電荷が失われてしまいます。このため、メモリセルから読み出したデータを一次的に(読み出しても消失しない)別の回路に保持し、読み出しが終わってから、保持しているデータをメモリセルに書き戻すことでデータの消失を防ぎます。この動作はプリチャージと呼ばれています。 Q43 RAS, CAS にアッパーライン(否定)が付いているのはなぜですか? A43 これら制御信号においては、しばしば、低電位のときオンとなるアクティブ・ローが用いられます。このように、低電位でオンとなることを明確にするためにアッパーライン(否定)が付いています。 Q44 DRAMではどうしてRASとCASを用いる必要があるのですか? A44 ここではクロックを用いない非同期のDRAMを想定しています。このような場合には、例えば、アドレス線から行アドレスを取得するタイミングを指定する必要があります。このためにRASの立ち下がりのタイミングを利用します。同様に、アドレス線から列アドレスを取得するタイミングを指定するためにCASを利用します。 Q45 最新のDRAMにおける高速化の工夫にはどのようなものがありますか? A45 クロックの立ち上がりと立ち下がりの両方で動作させることで2倍の動作速度を実現するDDR (double data rate) SDRAMや、同期クロックを高速化するDDR2, DDR2 SDRAM といった方式が利用されています。 Q46 フォンノイマン型ではないコンピュータとはどのようなものですか? A46 人間の脳をモデルとするニューロコンピュータ、データの流れに注目するデータフローの原理に基づくコンピュータなどの様々な試みがあります。 Q47 命令の長さは32ビット程度と説明されていますが、32ビット以外にどのような形式がありますか? A47 組込みで用いられるプロセッサでは、16ビットで1つの命令を指定するものもあります。また、命令の種類によって命令の長さが変わるプロセッサもあります。これらは命令セットアーキテクチャによって決められています。 Q48 算術論理演算命令、メモリ操作命令、分岐命令の他にどのような命令があるのですか? A48 多くのプロセッサは浮動小数点演算のための命令を持っています。また、近年の高性能プロセッサはマルチメディア処理を高速に処理するための命令を備えるようになっています。 Q49 命令フェッチは1つの命令を読み出すと説明されていますが、複数の命令を同時に読み出す(フェッチする)ことはないのですか? A49 近年のプロセッサは、高い性能を得るために複数の命令を同時にフェッチしています。従来のプロセッサとの命令セットアーキテクチャの互換性を維持しながら、同時に多くの命令をフェッチして、処理することにより高速化を達成するプロセッサはスーパースカラプロセッサと呼ばれることがあります。 Q50 命令メモリとデータメモリとして個別のメモリが用いられていますが、1つのメモリを共有して利用してはいけないのですか? A50 1つのメモリを共有して利用することも可能です。ただし、命令メモリとデータメモリでは要求が異なったり(命令メモリのデータが更新されることはない)、異なるメモリを用いることで同時に命令とデータを供給できるといった利点などから、図に示す構成をとることが一般的です。この様に、命令メモリとデータメモリが異なる構成をとるプロセッサのことをハーバード・アーキテクチャと呼ぶことがあります。 Q51 パイプライン処理とは何ですか? A51 プロセッサにおけるパイプライン処理とは、幾つかの命令を少しずつずらして並行的に処理することで、プロセッサの高速化を狙う方式です。近年の高性能プロセッサのほとんどが採用しています。

|